A Huawei acaba de registrar uma patente revelando um processo novo e exclusivo para a produção de chips avançados. A patente se concentra em superar uma das limitações da tecnologia de fotolitografia ultravioleta profunda (UVP), numa tentativa de competir com as máquinas ultravioleta extremas (EUV), às quais a China ainda não tem acesso. No entanto, existem muitas incertezas em torno disso.

A patente

A Huawei submeteu formalmente a documentação técnica ao escritório de patentes chinês em junho de 2022, o que lhe permitiu "proteger" a invenção. O conteúdo detalhado do estudo foi divulgado em janeiro de 2025, mas só agora veio à tona. O pedido de patente está pendente, ainda não foi concedido. O escritório de patentes está atualmente examinando o pedido para determinar se ele atende aos requisitos.

Por que isso importa?

Esta patente aborda as limitações do chamado Erro de Posicionamento de Borda (EPE, Edge Placement Error) no processo de interconexão avançado usado na fabricação de chips de última geração. O método descoberto, em teoria, possibilita o uso de "espaçamentos entre linhas metálicas" inferiores a 21 nm, mesmo utilizando a tecnologia ultravioleta profunda (UVP) em vez da ultravioleta extrema (EUV), que atualmente é a tecnologia fotolitográfica mais avançada... e à qual fabricantes chineses como a Huawei não têm acesso. Se atingirem seu objetivo, a empresa poderá, por exemplo, ter acesso a chips que, em teoria, poderiam competir com chips fabricados usando fotolitografia de 2 nm.

Espaçamento entre linhas metálicas?

Este termo se refere à distância mínima entre as linhas metálicas que formam as interconexões dentro do circuito integrado, ou, neste caso, do chip. Essas linhas transportam energia e sinais de dados entre os transistores, e esse espaçamento entre linhas metálicas é extraordinariamente pequeno para nós tecnológicos avançados.

O objetivo da patente é justamente viabilizar a fabricação dessas linhas com espaçamentos menores que 21 nm. Isso abre caminho para um processo potencial que poderia competir com a fotolitografia UVE de 2 nm usada pela TSMC, por exemplo. A palavra-chave aqui é "poderia".

Erro de Posicionamento de Borda (EPE)

O EPE é o erro que ocorre quando um padrão em um chip não é posicionado exatamente onde o projeto do chip pretendia. Quanto menor o espaçamento entre os metais, menor deve ser a margem de EPE para evitar que as linhas se toquem e causem um curto-circuito. Nessa escala, resolver esse problema é incrivelmente complexo, e a patente da Huawei propõe uma maneira de alcançá-lo.

Aprimorando a litografia "antiga"

Esse método permite que a fotolitografia UVP, menos poderosa e avançada que a UVE, seja usada para competir com ela. Permitiria, ainda, "contornar" as limitações que esse processo enfrenta atualmente, que normalmente tem dificuldades para ir além de 21 nm.

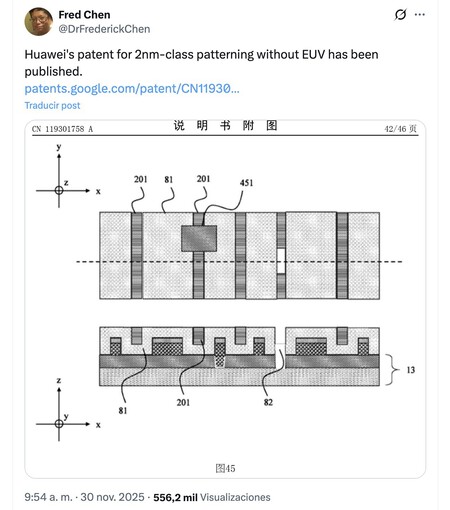

Está sendo introduzido um processo de máscara rígida dupla, utilizando dois materiais e um esquema de padronização especial que, teoricamente, permite a micronização abaixo de 21 nm e até mesmo abaixo de 5 nm - o que já é muito difícil de alcançar com a micronização UV.

Em resumo: a China poderia produzir chips avançados sem precisar usar as máquinas mais avançadas da ASML, às quais não tem acesso.

Porém...

Embora a técnica pareça impressionante, existem dois grandes problemas. O primeiro e mais importante é que se trata apenas de uma patente, o que não significa que o processo possa ser implementado na prática. As dificuldades para tal são enormes, o que nos leva ao segundo problema: a eficiência de produção seria, provavelmente, muito baixa e o rendimento (taxa de sucesso do processo) seria severamente afetado.

Em outras palavras, de todos os chips teoricamente produzidos com essa técnica, apenas uma pequena fração seria utilizável, resultando em um enorme desperdício do investimento.

Ver 1 Comentários