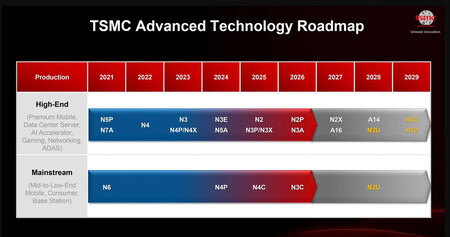

A TSMC revelou quais processos de fotolitografia estarão prontos para a fabricação em massa de chips nos próximos três anos. A maior fabricante de semicondutores do mundo anunciou oficialmente seu roteiro tecnológico durante o Simpósio de Tecnologia da América do Norte, realizado em Santa Clara, Califórnia, na última semana. As tecnologias apresentadas destacam uma realidade inegável: a empresa taiwanesa está determinada a manter sua liderança na indústria de fabricação de circuitos integrados.

Para alcançar esse objetivo, até 2029, a TSMC terá suas tecnologias de integração A12 e A13 prontas para produção em massa. Essas tecnologias são simplesmente derivadas de sua fotolitografia A14. Do ponto de vista comercial, essas serão as primeiras tecnologias de 1,2 nm e 1,3 nm da TSMC, embora seja importante que os usuários se lembrem de que os nanômetros não refletem mais com precisão o comprimento das portas lógicas ou outros parâmetros físicos, como a distância entre os transistores.

Cada fabricante de chips lida com essas medidas com considerável liberdade, o que impede que os usuários comparem diretamente as litografias que estão tentando nos "vender". A discrepância entre a nomenclatura e a realidade física dos circuitos integrados é agora quase absoluta, mas os nanômetros continuam sendo úteis para identificar o estágio de desenvolvimento de cada fotolitografia dentro do portfólio de cada fabricante de semicondutores. Dito isso, vale a pena analisar mais de perto o que a TSMC está preparando.

Façanha técnica: A12 e A13 sem a necessidade das máquinas High-NA da ASML

Kevin Zhang, vice-diretor de operações da TSMC, esclareceu algo muito importante: "Estou impressionado com nossa equipe de P&D. Eles continuam encontrando maneiras de impulsionar o desenvolvimento tecnológico sem usar as máquinas High-NA UVE da ASML. Algum dia talvez tenhamos que usá-las, mas agora podemos continuar a colher os benefícios da tecnologia UVE atual sem migrar para High-NA, que, como todos sabemos, é extremamente cara." É impressionante. A TSMC continuará desenvolvendo litografias altamente competitivas pelos próximos três anos sem precisar recorrer às máquinas High-NA.

No slide abaixo, podemos ver que, em 2028, o nó litográfico mais avançado da TSMC para o mercado consumidor será o A14, que utilizará transistores GAA (Gate-All-Around) de segunda geração. A produção em massa de chips para o consumidor usando a litografia A13 começará em 2029 e será baseada na tecnologia de integração A14. Isso significa simplesmente que a litografia A13 será o resultado de um aprimoramento da A14.

De acordo com a TSMC, a tecnologia de integração A13 é uma otimização óptica da A14, que na prática permitirá atingir uma densidade de transistores 6% maior, mantendo a compatibilidade entre as duas. Além disso, a litografia N2U, também voltada para o mercado consumidor, chegará em 2028. Ela será uma extensão da plataforma N2 (2 nm) e oferecerá, ainda segundo as previsões da TSMC, um desempenho entre 3% e 4% superior ao da N2P, bem como um consumo de energia entre 8% e 10% menor.

Por fim, a litografia A12 chegará em 2029 juntamente com a A13, embora seja destinada principalmente a chips para data centers. Assim como a A13, ela utilizará transistores GAA de segunda geração e a tecnologia NanoFlex Pro. Esta última tecnologia permitirá que os projetistas de circuitos integrados utilizem células rápidas para as partes críticas da GPU que necessitam de alta velocidade e células densas ou eficientes para o restante, otimizando assim a área do chip até o último milímetro. O NanoFlex Pro é uma das inovações com as quais a TSMC pretende proteger sua liderança tecnológica, para que seus clientes de chips de inteligência artificial (IA), como Nvidia, AMD e Cerebras, continuem a confiar nela e não na Samsung ou na Intel.

Imagem | TSMC

Mais informações | TSMC | Tom's Hardware

Ver 0 Comentários